Dlaczego warto używać Xilinx FPGA XC3S500E-4FTG256I?

Jeśli jesteś projektantem elektroniki, być może znasz układ XC3S500E-4FTG256I .

Ta macierz programowalnych bramek (FPGA) jest szeroko stosowana w różnych zastosowaniach, od elektroniki użytkowej po sterowanie przemysłowe, lotnictwo, wojsko i inne dziedziny.

Układ FPGA to urządzenie półprzewodnikowe składające się z matrycy konfigurowalnych bloków logicznych (CLB), połączonych programowalnymi połączeniami. Użytkownik określa te połączenia poprzez programowanie pamięci SRAM. CLB może być prosty (bramki AND, OR itp.) lub złożony (blok pamięci RAM). Układ FPGA umożliwia wprowadzanie zmian w projekcie nawet po wlutowaniu urządzenia w płytkę drukowaną.

W tym artykule poznasz pewne podstawy XC3S500E-4FTG256I firmy Xilinx, a także poznasz profesjonalny sposób jego wykorzystania i jego funkcji.

Co to jest XC3S500E-4FTG256I?

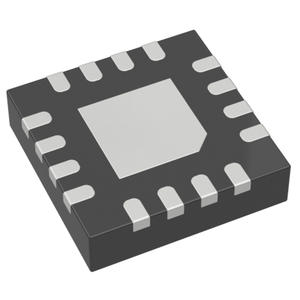

XC3S500E-4FTG256I należy do serii Spartan-3E FPGA, zaprojektowanej przez Xilinx.

Rodzina Spartan-3E oferuje ekonomiczne rozwiązanie FPGA o niskim poborze mocy , wysokiej wydajności i zaawansowanych funkcjach na poziomie systemu.

Xilinx Zynq FPGA

XC3S500E-4FTG256I posiada 500 000 bramek systemowych, 772 wejść/wyjść użytkownika i 36 bloków pamięci RAM.

Działa z maksymalną częstotliwością 400 MHz i ma zakres napięcia rdzenia od 1,14 V do 1,26 V.

XC3S500E-4FTG256I jest powszechnie używany w zastosowaniach takich jak przemysł lotniczy i obronny, motoryzacyjny, nadawczy, konsumencki, obliczenia dużej wydajności, przemysłowy, medyczny i naukowy, testowy i pomiarowy.

Poproś o oryginał i nowy Xilinx XC3S500E-4FTG256I FGPA teraz

Właściwości XC3S500E-4FTG256I

• Sygnalizacja SelectIO

- Do 633 pinów we/wy

- Osiemnaście standardów sygnału single-ended

- Osiem standardów sygnału różnicowego, w tym LVDS i RSDS

- Obsługa podwójnej szybkości transmisji danych (DDR)

• Zasoby logiczne

- Duża liczba komórek logicznych z możliwością rejestracji przesuwnej

- Szerokie multipleksery

- Szybka logika przenoszenia z wyprzedzeniem

- Dedykowane mnożniki 18 x 18

- Logika JTAG zgodna z IEEE 1149.1/1532

• Pamięć hierarchiczna SelectRAM

- Do 1728 Kbitów całkowitego bloku RAM

- Do 432 Kbitów całkowitej rozproszonej pamięci RAM

• Menedżer zegara cyfrowego (cztery DCM)

- Eliminacja przekrzywienia zegara

- Synteza częstotliwości

- Przesunięcie fazowe o wysokiej rozdzielczości

English

English Español

Español Português

Português русский

русский français

français 日本語

日本語 Deutsch

Deutsch Tiếng Việt

Tiếng Việt Italiano

Italiano Nederlands

Nederlands ไทย

ไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা

বাংলা Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türk

Türk Gaeilge

Gaeilge عربى

عربى Indonesia

Indonesia norsk

norsk čeština

čeština Ελληνικά

Ελληνικά Українська

Українська Javanese

Javanese فارسی

فارسی български

български ລາວ

ລາວ Latine

Latine Қазақ

Қазақ Euskal

Euskal Azərbaycan

Azərbaycan slovenský

slovenský Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski Српски

Српски 简体中文

简体中文 繁体中文

繁体中文 Беларус

Беларус